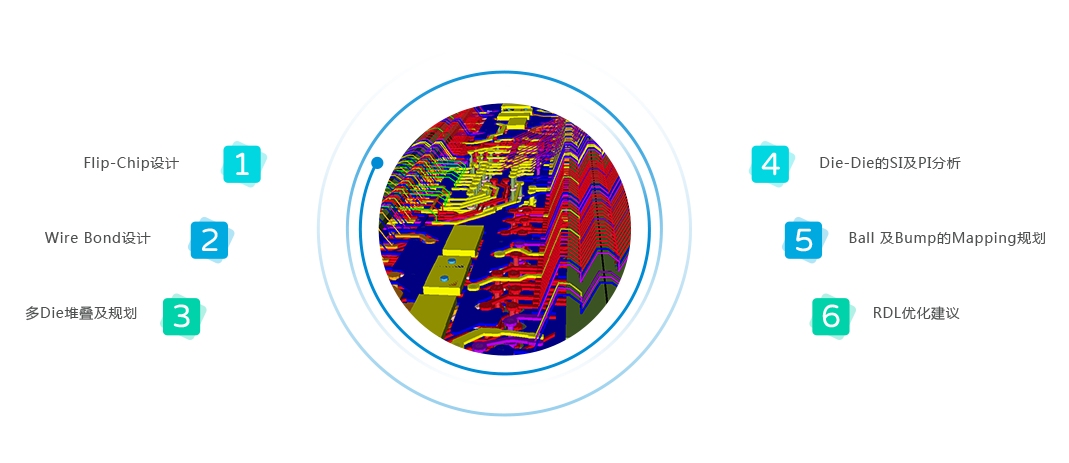

SiP設計(jì)能力

SiP設計優勢

- 芯片-封裝-係統協同規劃與設計

- 仿真與設計同步進行

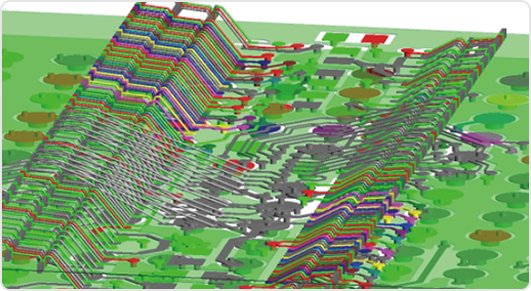

- Wire Bond 3D建模

- 仿真精度高,優化準(zhǔn)確

- 熟悉主流的封裝基板(bǎn)生產工藝

- Hspice模型轉IBIS模型

- 可協助生成設計指導書

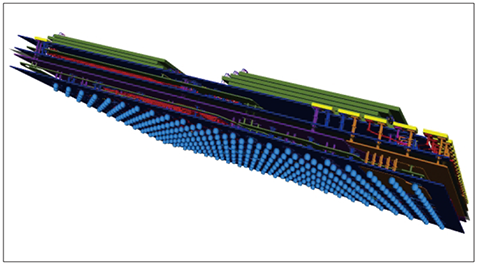

SiP設計案例(lì)展示

- 9個(gè)DDR4顆粒,4+5層堆疊

- DDR4運行速(sù)率3200Mbps

- 整體性能媲美SO-DIMM

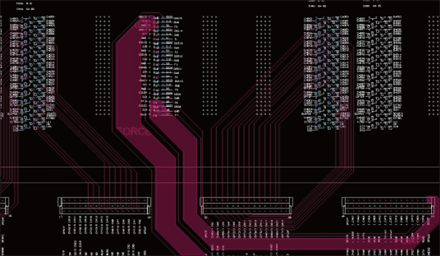

ATE能力介紹

- 待測試芯片(piàn)pin數多,多達(dá)幾千pin

- 疊層(céng)多達(dá)40層(céng)以(yǐ)上, 板厚超過5mm

- 走線和過孔的設計(jì)和加工趨於極限能力(lì)

- 需要(yào)進行精確仿真來保證(zhèng)走(zǒu)線不會影響芯片測試精度