EDSFF單板設計案例

發布時(shí)間:2025-10-06 08:36:08

|

類別 |

EDSFF(Enterprise &Datacenter Storage Form Factor) |

|

產品所屬行業 |

存儲 |

|

主要芯片 |

CPU:CNX-2660_2670-AA DDR4:DDR4_SDP_DDP_BGA78_BGA78_0808_1 NAND:NAND_2CH_BGA152

|

|

單板類型 |

SSD |

|

Pin數(shù) |

8564 |

|

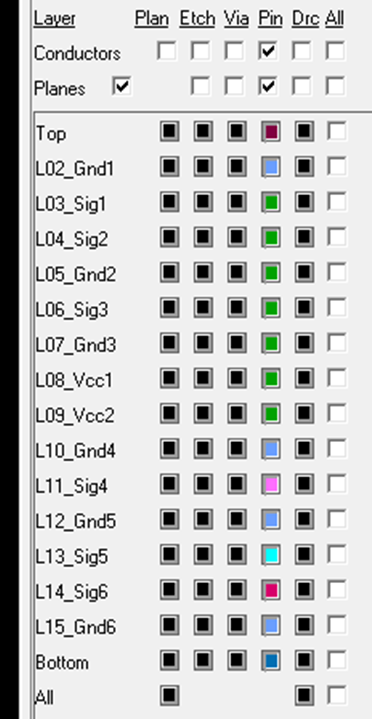

層數(shù) |

16 |

|

最高信(xìn)號速率 |

8Gb/s |

|

難點 |

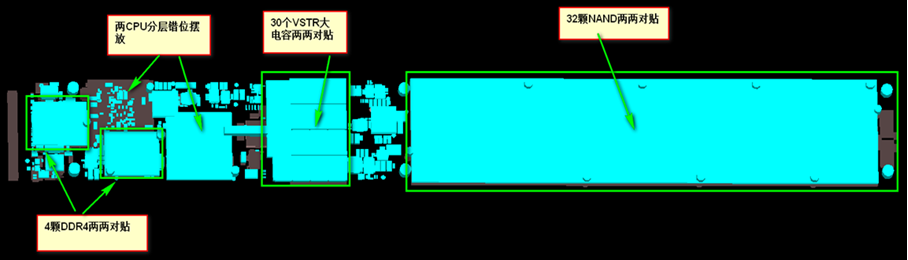

1、 布局較密(Pin Density(pins/sq in)達260),雙(shuāng)CPU,每個CPU各帶2片DDR4顆粒和16片NAND,且客戶希望盡量多的增加VSTR大電容的個數; 2、 板框為長條形的,布局布線空(kōng)間(jiān)受限;板(bǎn)厚限製為1.57mm,布線需求要做到16層,層疊設計比較極限; 3、 多方溝通(客(kè)戶(hù),板廠,公司內部),且有語言差異; |

|

我司對策 |

1、嚐(cháng)試不同方案的布局,通孔設計或者盲埋孔設計等,並與客戶、工廠多方溝通,最(zuì)終(zhōng)確定: Ø 通孔設計,減少成本; Ø BGA不考慮預留返修(xiū)區; Ø 2個CPU放(fàng)在不同層麵錯開擺放(fàng); Ø 所有VSTR大電容、DDR顆粒和NAND顆粒兩兩對(duì)貼擺放;

2、考慮單板的走線和電源(雙CPU,每個CPU各帶2片DDR4顆(kē)粒和(hé)16片NAND),因單板空間限製,需要6個走線層和2個(gè)電源(yuán)層;板(bǎn)厚1.57mm,考慮單板和信號線的參考平麵,通過和板廠(chǎng)溝通,最終確定16層,6個內層走線的層疊。這個層疊的不(bú)足之處為層間距比較小,走線線寬較細,且存在(zài)相鄰層,對信號(hào)質量會有一定影響,增加布線難度。

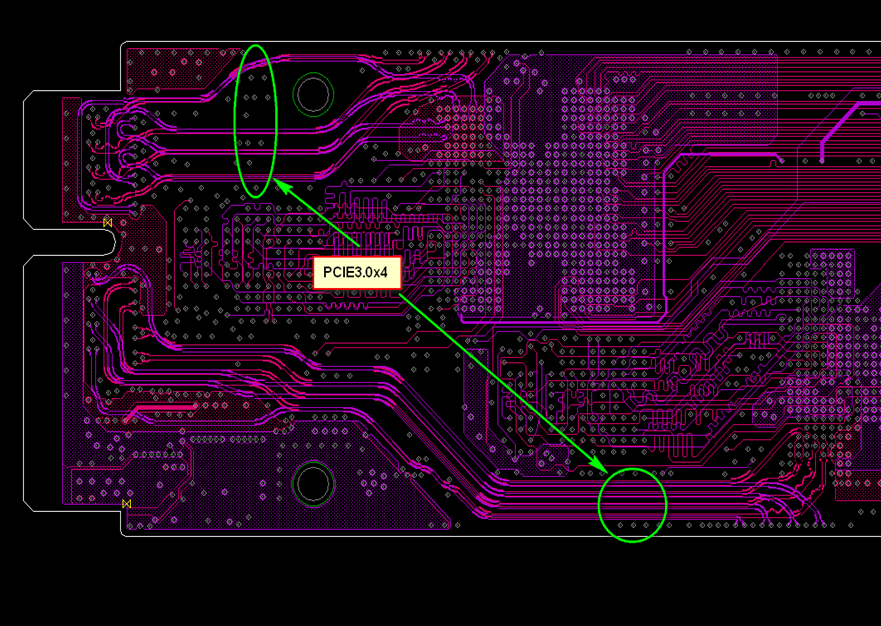

3、增加溝(gōu)通效率: Ø 除常規的電話、郵件溝通外,重要節點、問題點安排工程師與客戶現場的溝通,做到溝通及時、有效; Ø 與板(bǎn)廠的配合由之前通過客戶和板廠溝通相關問題、然後把結果轉達給(gěi)設計工程(chéng)師這種(zhǒng)中(zhōng)轉的方式,改為設計工程師直(zhí)接和板廠方麵(miàn)溝通,同樣有效的(de)提升溝通效率,助(zhù)力項目(mù)順利開(kāi)展; Ø SI人員參與,對重要信號進行仿真和優化(huà),並對PCIE信號做背鑽處理,提升信號質(zhì)量;

|