高速PCB板DDR5數據信號的長STUB要背鑽嗎?

發布時間:2025-10-06 11:41:39

高速先生成員:周(zhōu)偉

上一(yī)篇(piān)文章 過孔Stub對ddrx地址信號的影(yǐng)響 提到過後(hòu)麵(miàn)會有stub對數據信號(hào)的影響(xiǎng),今天我們就一起來看看吧。

前文通過幾個仿真例子看到,長stub對3200Mbps以內的DDRx地(dì)址信號來(lái)說有一(yī)定的(de)好處,對於速率不是那麽高的信號(不超過8Gbps),如DDR4、DDR5甚至LPDDR5,我(wǒ)們是否可以(yǐ)把這個結論再(zài)擴展到速率更高的數據信號上呢?於是我(wǒ)們又做了如下一些仿真來看看長(zhǎng)短stub在更高速率的數據上的一些對比。

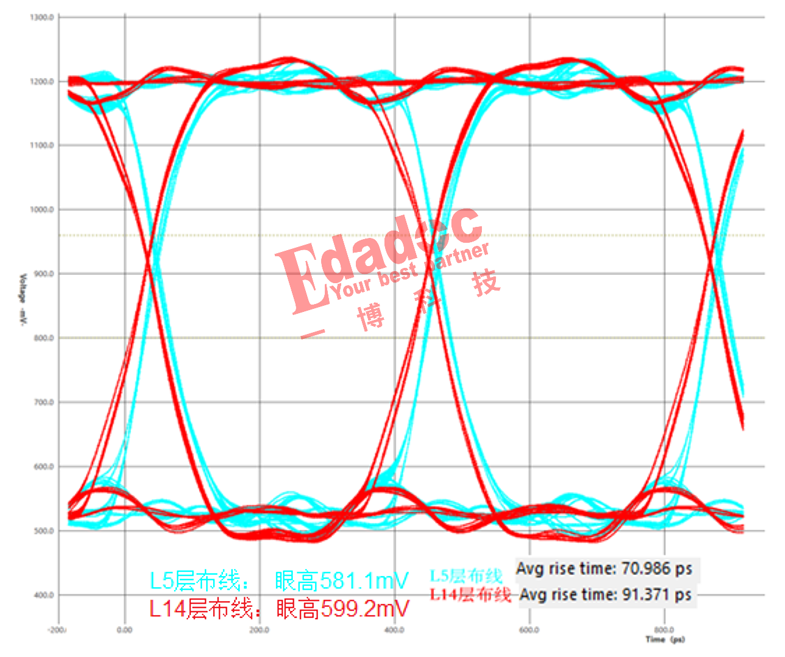

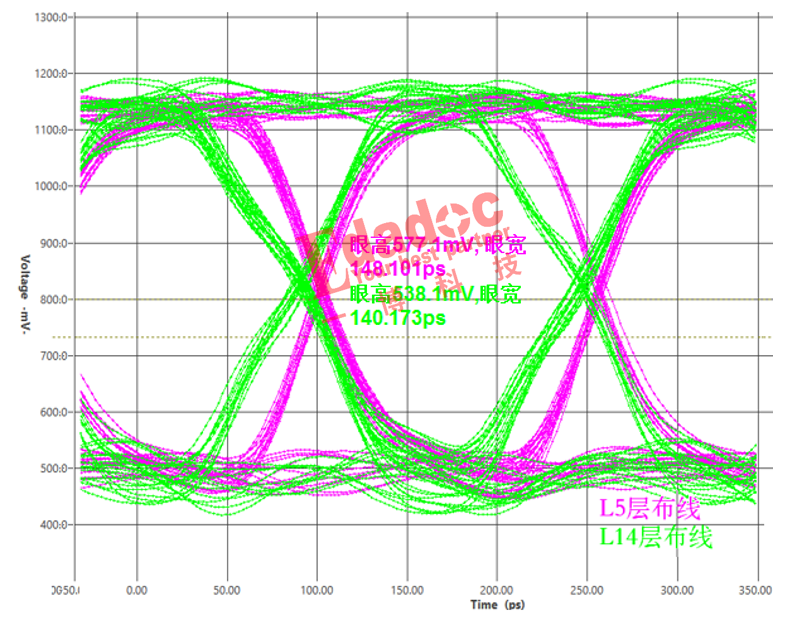

還是上(shàng)文同樣的疊層和驅動,接收采用ODT60,在數據率為2400Mbps的時候(hòu)仿真出(chū)來的數據眼圖如下圖1所示。

圖1 速率2400Mbps時(shí)數(shù)據信號寫眼圖

紅(hóng)色L14層(céng)走線的眼圖看起來眼高更高(gāo),jitter也小點,對(duì)應的斜率(lǜ)也大(dà)一點,說明長stub對數據信號在2400Mbps的速率下基本沒什麽影響,甚至還會(huì)稍微好(hǎo)點。進一(yī)步把(bǎ)速率(lǜ)提(tí)高到3200Mbps,其他不變的情況下長短stub的眼圖仿真結果如下圖2所示。

圖2 速(sù)率3200Mbps時數據信號寫眼圖

可以看到速率上來之後,短stub的優勢慢慢開始體現(xiàn)出來了,眼(yǎn)高和眼寬都稍微(wēi)比長stub的布線層信號要好(hǎo)。

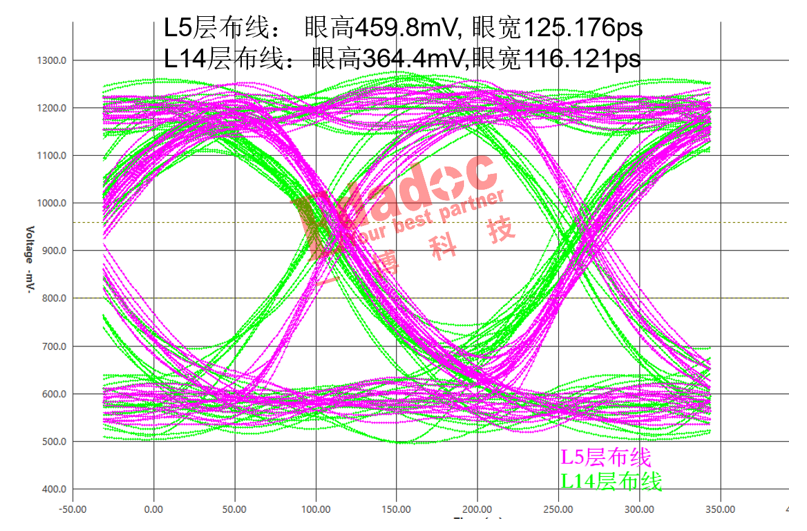

我(wǒ)們接下來再看看DDR5 6400Mbps速率的情況,於是其他條件都不變,隻是將速率提升到6400Mbps,顆粒模型(xíng)也換成支持DDR5的,仍然采用ODT60的端接,仿真後波(bō)形如下圖3所(suǒ)示。

圖3 速率6400Mbps時數據信號寫眼(yǎn)圖

從仿真(zhēn)結果可以看(kàn)出,速率提升到6400Mbps時,長stub的L14層走線信號眼圖急劇變差,眼高和眼寬都明顯(xiǎn)小於短stub的L5層走線,說明DDR5的數據信號還是要(yào)適當考慮stub的影響,PCB設計時就要考慮stub較短的層麵。

同時我們又驗證了某廣泛使用的FPGA支持DDR5信(xìn)號(hào)的模型,在其他不變(biàn)的情況下隻是換了主控的模(mó)型,仿真結果如下圖4所示。

圖4 另一驅(qū)動速率6400Mbps時數據信(xìn)號寫眼圖

換了驅動後(hòu),仿真結論還是一樣的,長stub的信號沿變(biàn)緩了很多,導致眼高(gāo)和眼寬都變小了。

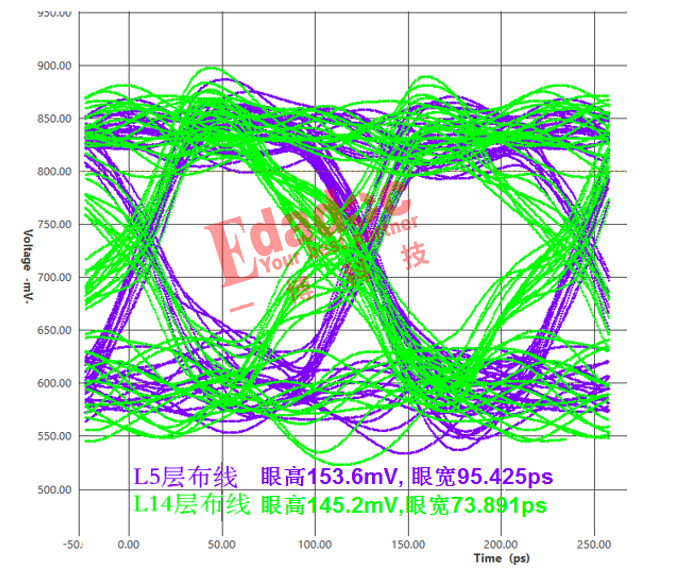

考慮到現在LPDDR5的應用也越來越多了,且我們也已經仿真過很多啦,接(jiē)下來我們就用LPDDR5模型(xíng)再來驗證一下長短Stub的影響。拓撲還是(shì)不變,驅動和接收(shōu)換成支持(chí)LPDDR5的模型(xíng),在數據速(sù)率8533Mbps 時不開均衡(héng)的仿(fǎng)真對比結果如下圖5所示。

圖5 速(sù)率8533Mbps時數據信號寫眼圖

可以看到有長stub的L14層信號的眼圖急劇變差,jitter變大(dà)了很多(duō),比短stub的L5層走線的信號眼高和眼寬都小了,裕量相對變少,說明速率越高後stub的影響(xiǎng)還是比較大,此時盡量保持短stub層走線,至於是否一(yī)定(dìng)要背鑽,還是要(yào)看情況,大多數情況下(xià)還是可以不用的,畢竟背鑽需要額外增加成本,可以優先走stub短的層。如果實在避免(miǎn)不了長stub的層,我們還是可(kě)以參考高速信號stub長度的經驗,當stub長度(單位mil)超過1.5倍的300/信(xìn)號速(sù)率(單位Gbps),盡量或必須背鑽。不考慮成本的情況下,當stub長度(單位mil)超過300/信號速率(單位Gbps)時就(jiù)可以做(zuò)背鑽了。