揭秘DC-BIAS效應:電容“縮水”對電源噪聲的影響

發布時間:2025-05-12 17:31:57

高(gāo)速先生成(chéng)員-- 黃剛

不可能吧?電容不還是那個電容嗎?為(wéi)什麽接到1V的直流電(diàn)壓(yā)時和接到3.3V的直(zhí)流電(diàn)壓效果會不一樣(yàng)?相信大多數粉絲都不(bú)知道這個point吧(ba)。的確,如果大家沒聽過DC-Bias這個名詞的話,估計是很難知道……

電容在電源網絡(luò)中的應用主要就是充當去耦電容了,我們知道從電源(yuán)芯片到(dào)用電芯(xīn)片的漫長的電源鏈路(lù)中,會存在著大大小小不一樣的電容。原理就不用我(wǒ)們再再再一次重複說明了吧?額,算了,再說一次吧,去耦電容的作用就是降低電源地之間的(de)阻(zǔ)抗,這樣的(de)話當用電端電流(liú)波動的時候,在用電芯片處產生的噪聲就會減小。

今天我們(men)就不過分的討論怎麽仿真電源(yuán)的(de)PDN阻抗這事(shì)了。關注點放在電容到底在不同的直流電源(yuán)中會不會有差異。什麽意思呢?就是同一個電容接不同的直流電源去使用的時候有沒有區別!DC-Bias翻譯成中文,那就是直流偏置。

那到底要(yào)怎麽知(zhī)道電(diàn)容的(de)直流偏置特性對它(tā)的影響呢?其實也(yě)沒那麽難了(le),隻是很多(duō)人沒有去做,那就是去翻翻它的datasheet不(bú)就有(yǒu)了嘛。例如某個(gè)常用的0402封裝,1uF的(de)電容。

再往下翻,就能看到它(tā)的DC-BIAS特性,如下(xià):

哇!原來直流電壓(yā)對電容容值的影響竟然如此的大!每增加1V的直流電壓,容值差不多要減(jiǎn)小10%!!!

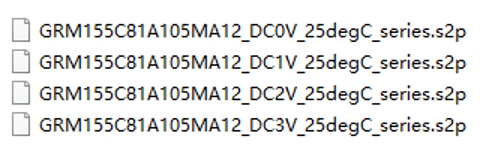

看起來是(shì)挺嚇人的哈(hā),不知(zhī)道實際上對PDN阻抗的影響有多大呢?這個點感覺會有更多粉絲想知道吧。那我們通(tōng)過一些渠道拿到了這個電容直流偏置電源0V、1V、2V到3V這4種case的S參數模(mó)型,就是(shì)下麵的4個模型了。

那我(wǒ)們分別來看看這幾種case下電容(róng)的PDN阻抗曲線的差異,就是(shì)下圖展示的一(yī)樣了。

感(gǎn)覺還好(hǎo)吧,基本上不就重合了嘛,沒啥差異啊?真的嗎?那是因為橫坐標和縱坐標都用了對數(shù)的形式來展示。我們分別放大兩(liǎng)個頻段的細節給大家(jiā)看看,就知(zhī)道了。

第一個是低頻時候的放大細節,如(rú)下。可以看到(dào)在低頻時,由於偏置電壓越(yuè)高,容值(zhí)越小,導致PDN阻抗(kàng)變大,而且變大的幅度還是很多(duō)的!

然後我們再來看看在諧振頻點附(fù)近的差異,直流偏置3V和0V來(lái)比,去耦諧振頻點差不多(duō)變化了2MHz,這其實是一個不算小的變化了。因為像板級(jí)電容的PDN阻抗優化,我們一般也就(jiù)關注到20MHz而已!

我們這篇文章簡單的介紹了(le)DC-Bias的原理並用了一個電容來驗證了(le)直流(liú)偏置對電容PDN阻抗的影響。當然目的就是讓大家了解到電(diàn)容放(fàng)在你手上(shàng)和焊在電路板中不同電壓的電源(yuán)網絡中是不一樣的哈,接入(rù)不同的直流電壓後,容值會發生變化,從而影響到PDN阻抗在低頻和諧振頻率的效果。那給我們設計或者仿真的啟發就是:如果對電源的PDN阻抗要求不是很高的情況下,不考慮偏置特性(xìng)倒不一定出問題;反過來,如果本身的PDN要求就很嚴格,那麽你就要嚴謹的去考(kǎo)慮它到底放到了1V還是2V的電源網絡中的情況了,因為從驗證結果上來看,不同電壓的PDN阻抗差異還是不能忽略的!